# Application Note 3225 Waking up a DS2761/DS2762

#### www.maxim-ic.com

#### Introduction

The DS2761 and DS2762 High Precision Battery Monitors provide monitoring and protection for a Li+ cell. These devices have two power modes: Active and Sleep. While in Active Mode, the devices continually monitor the system and provide Li+ protection. While in Sleep Mode, these activities cease.

There are several conditions that can transition the devices from Active Mode into Sleep Mode: a low DQ, an under voltage condition, and the issuing of the Swap command. There is another set of conditions that can transition the devices from Sleep Mode into Active Mode: a rising edge of DQ, a falling edge of PS, attaching a charger, and the issuing the Swap Command. The state of the PMOD bit, SWEN bit, DQ pin, and battery voltage effect how the Charge Control (CC) and Discharge Control (DC) pins react when waking up. This Application Note provides details of what happens in all possible waking up scenarios.

# Transitioning from Sleep to Active Mode

Table 1 contains all of the combinations of transitioning a DS2761/DS2762 from Sleep Mode to Active Mode. The 'Sleep Mode' column indicates the manner in which the device was transitioned into Sleep Mode. 'PMOD' indicates that PMOD was 1 and DQ was low for 2 seconds. 'UV' indicates that the cell voltage was below the under voltage threshold ( $V_{UV}$ ). 'Swap Command' indicates that SWEN was 1 and the Swap Command was issued to a different Net Address than the device under test.

The 'Exit Trigger' column indicates what caused the device to transition from Sleep Mode to Active Mode. The four methods that can cause a device to wake up are: a rising edge of DQ when PMOD is 1 and SWEN is 0, a falling edge of PS, attaching a charger when SWEN is 0, and issuing the Swap Command to the Net Address of the device under test when the SWEN bit is set.

The 'Pre-Sleep Conditions' indicate the settings of the PMOD and SWEN bits of the Status Register, the DQ line and the cell voltage in relation to  $V_{UV}$ .

The EEPROM and shadow RAM of the device is not disturbed when transitioning from Active Mode to Sleep Mode or from Sleep Mode to Active Mode.

Each case outlined in Table 1 is described below with an associated waveform. Some cases have a second waveform, which show the device re-entering Sleep Mode after a period of time because a condition that will cause a device to go to Sleep Mode still exists.

| ble 1. Conditions for transitioning from Sleep mode to Active mode |      |              |                    |                      |      |    |                 |

|--------------------------------------------------------------------|------|--------------|--------------------|----------------------|------|----|-----------------|

|                                                                    | Case | Sleep Mode   | Exit Trigger       | Pre-Sleep Conditions |      |    |                 |

|                                                                    |      |              |                    | PMOD                 | SWEN | DQ | V <sub>IN</sub> |

|                                                                    | А    | PMOD         | Rising Edge of DQ  | 1                    | 0    | 0  | $> V_{UV}$      |

|                                                                    | В    | PMOD         | Falling Edge of PS | 1                    |      | 0  | $> V_{UV}$      |

|                                                                    | С    | PMOD         | Attach a Charger   | 1                    | 0    | 0  | $> V_{UV}$      |

|                                                                    | D    | UV           | Rising Edge of DQ  | 1                    | 0    |    | $< V_{UV}$      |

|                                                                    | Е    | UV           | Falling Edge of PS |                      |      |    | $< V_{\rm UV}$  |

|                                                                    | F    | UV           | Attach a Charger   | 0                    | 0    | 0  | $< V_{\rm UV}$  |

|                                                                    | G    | UV           | Attach a Charger   |                      | 0    | 1  | $< V_{\rm UV}$  |

|                                                                    | Н    | UV           | Attach a Charger   | 1                    | 0    | 0  | $< V_{\rm UV}$  |

|                                                                    | Ι    | UV           | Swap Command       |                      | 1    | 1  | $< V_{\rm UV}$  |

|                                                                    | J    | Swap Command | Falling Edge of PS | 0                    | 1    |    | $> V_{\rm UV}$  |

|                                                                    | Κ    | Swap Command | Falling Edge of PS | 1                    | 1    | 0  | $> V_{\rm UV}$  |

|                                                                    | L    | Swap Command | Falling Edge of PS | 1                    | 1    | 1  | $> V_{\rm UV}$  |

|                                                                    | М    | Swap Command | Swap Command       |                      | 1    | 1  | $> V_{\rm UV}$  |

# Table 1. Conditions for transitioning from Sleep Mode to Active Mode

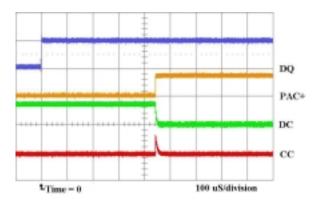

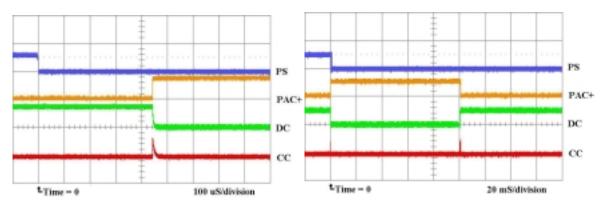

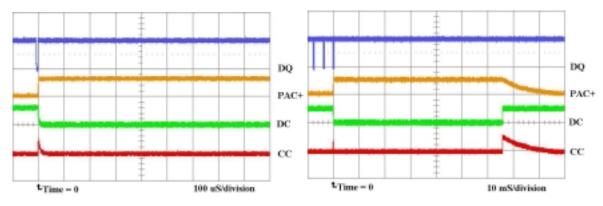

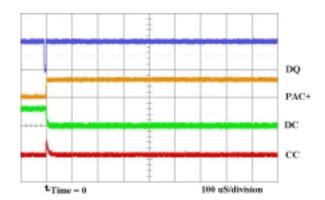

#### Case A: PMOD Sleep, Rising Edge of DQ, PMOD = 1, SWEN = 0, DQ = 0, Cell > $V_{UV}$

If PMOD is 1, SWEN is 0 and the cell voltage is above  $V_{UV}$ , then a rising edge of the DQ line causes the device to enter Active Mode 450µs later. The DC pin is pulled to the cell voltage while in Sleep Mode, which disables PAC+. The CC pin is pulled to PAC+, so it is low when PAC+ is disabled. When the device enters Active Mode, CC and DC are driven low, which enables PAC+.

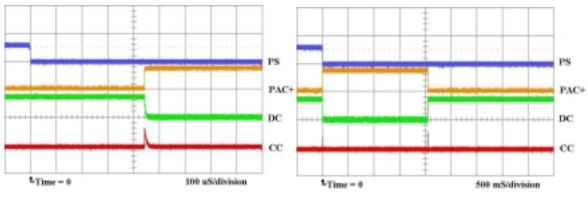

# Case B: PMOD Sleep, Falling Edge of PS, PMOD = 1, DQ = 0, Cell > $V_{UV}$

If PMOD is 1, DQ is low, and the cell voltage is above  $V_{UV}$ , then a falling edge on the PS pin causes the device to enter Active Mode in 450µs. The pins react the same as Case A. However, because the PMOD bit is 1 and DQ is still low, the device re-enters Sleep Mode after 2s. At that time, DC is pulled to the cell voltage, which disables PAC+. The CC pin is pulled to PAC+.

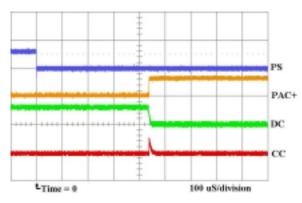

#### Case C: PMOD Sleep, Attach a Charger, PMOD = 1, SWEN = 0, DQ = 0, Cell > V<sub>UV</sub>

If PMOD is 1, SWEN is 0, DQ is low, and the cell voltage is above  $V_{UV}$ , then the device enters Active Mode 450µs after a charger is connected. In this case, PAC+ is now high because of the charger connection, so CC is pulled high while in Sleep Mode. Once in Active Mode, CC and DC are driven low, which enables PAC+. However, because PMOD is 1 and DQ is low, the device re-enters Sleep Mode after 2s. Then, the device will again see that a charger is connected and wake up. This cycle repeats every 2s, with PAC+ being disabled for 450µs and enabled for 2s.

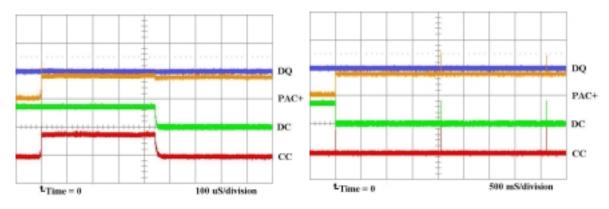

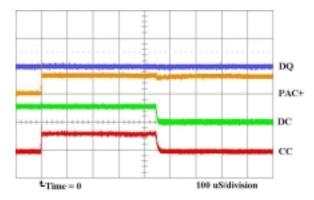

#### Case D: UV Sleep, Rising Edge of DQ, PMOD = 1, SWEN = 0, Cell < $V_{UV}$

If the cell voltage is below  $V_{UV}$ , PMOD is 1, and SWEN is 0, then a rising edge on the DQ line causes the device to enter Active Mode in 450 $\mu$ s. However, the device detects the under voltage condition and goes back to sleep 100ms after waking up.

#### Case E: UV Sleep, Falling Edge of PS, Cell < V<sub>UV</sub>

If the cell voltage is below  $V_{UV}$ , then a falling edge on the PS pin causes the device to enter Active Mode in 450µs. However, the device detects the under voltage condition and goes back to sleep 100ms after waking up.

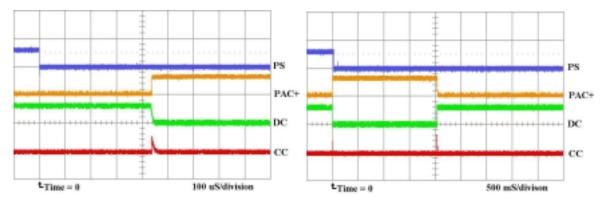

#### Case F: UV Sleep, Attach a Charger, PMOD = 0, SWEN = 0, DQ = 0, Cell < $V_{UV}$

If the cell voltage is below  $V_{UV}$ , PMOD is 0, SWEN is 0 and DQ is low, then the device entesr Active Mode 450µs after a charger is connected. The DC pin was high before the charger was connected because of the under voltage condition. The CC pin is pulled to PAC+, so it goes high when the charger is connected to PAC+, and stays high until the device enters Active Mode, at which time both pins are driven low.

#### Case G: UV Sleep, Attach a Charger, SWEN = 0, DQ = 1, Cell < $V_{UV}$

If the cell voltage is below  $V_{UV}$ , SWEN is 0 and DQ is high, then the device enters Active Mode 450 $\mu$ s after a charger is connected. The pins react the same as Case F.

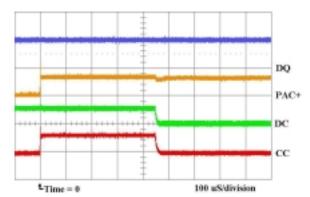

# Case H: UV Sleep, Attach a Charger, PMOD = 1, SWEN = 0, DQ = 0, Cell < $V_{UV}$

If the cell voltage is below  $V_{UV}$ , PMOD is 1, SWEN is 0 and DQ is high, then the device enters Active Mode 450µs after a charger is connected. The pins react the same as Case F for the first 2s. However, because PMOD is 1 and DQ is low, the device re-enters Sleep Mode after 2s. Then, the device will again see that a charger is connected wake up. This cycle will repeat every 2s, with PAC+ being disabled for 450µs and enabled for 2s.

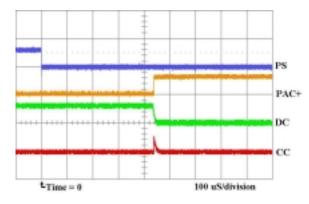

#### Case I: UV Sleep, Swap Command, SWEN = 1, DQ = 1, Cell < V<sub>UV</sub>

If the cell voltage is below  $V_{UV}$ , SWEN is 1, and DQ is high, then the device enters Active Mode on the next rising edge of DQ following a Swap Command to the Net Address of the device under test. Both CC and DC are driven low immediately, which enables PAC+. However, the device detects the under voltage condition and goes back to sleep 65ms after waking up.

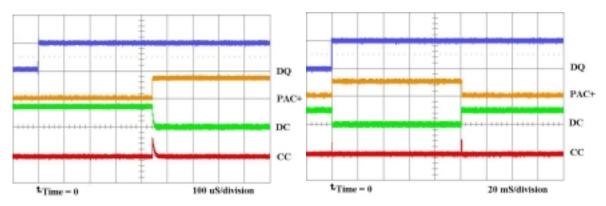

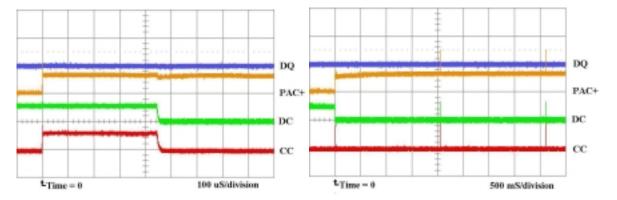

#### Case J: Swap Command Sleep, Falling Edge of PS, PMOD = 0, SWEN = 1, Cell > $V_{UV}$

If the device has been swapped into Sleep Mode, SWEN is 1, PMOD is 0, and the cell voltage is above  $V_{UV}$ , then the device enters Active Mode 450µs after a falling edge on PS. The DC pin is pulled to the cell voltage while in Sleep Mode, which disables PAC+. The CC pin is pulled to PAC+, so it is low when PAC+ is disabled. When the device enters Active Mode, CC and DC are driven low, which enables PAC+.

**Case K:** Swap Command Sleep, Falling Edge of PS, PMOD = 1, SWEN = 1, DQ = 0, Cell >  $V_{UV}$ If the device has been swapped into Sleep Mode, SWEN is 1, PMOD is 1, DQ is low, and the cell voltage is above  $V_{UV}$ , then the device entesr Active Mode 450µs after a falling edge on PS. The pins react the same as Case J for the first 2s. However, because PMOD is 1 and DQ is low, the device reenters Sleep Mode after 2s.

**Case L:** Swap Command Sleep, Falling Edge of PS, PMOD = 1, SWEN = 1, DQ = 1, Cell >  $V_{UV}$ If the device has been swapped into Sleep Mode, SWEN is 1, PMOD is 1, DQ is high, and the cell voltage is above  $V_{UV}$ , then the device enters Active Mode 450µs after a falling edge on PS. The pins react the same as Case J.

#### Case M: Swap Command Sleep, Swap Command, SWEN = 1, DQ = 1, Cell > $V_{UV}$

If the device has been swapped into Sleep Mode, SWEN is 1, and DQ is high, and the cell voltage is above  $V_{UV}$ , then the device enters Active Mode on the next rising edge of DQ following a Swap Command to the Net Address of the device under test. Both CC and DC are driven low immediately, which enables PAC+.

# Summary

The DS2761/DS2762 can be transitioned from Sleep Mode to Active Mode using one of four methods: a rising edge of DQ, a falling edge of PS, attaching a charger, or issuing the Swap command. Each method requires a certain set of conditions to be true in order to wake the device up. Some cases allow the device to wake up momentarily, only to go back to sleep because a condition that pust it into Sleep Mode still exists. This Application Note also applies to the C2 Revision of the DS2760.